ADC 与 DAC 基础知识

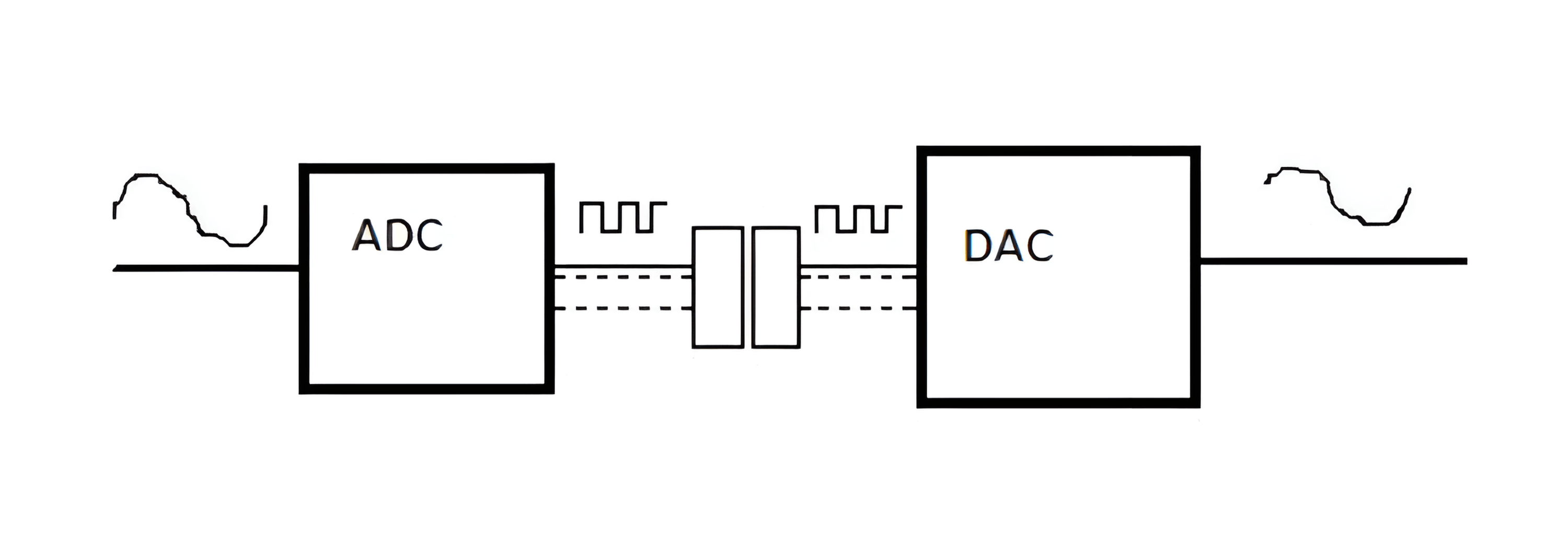

在现实世界中,常见的信号大都是模拟量,像温度、声音、气压等,但在信号的处理与传输中,为了减少噪声的干扰,较多使用的是数字量。因此我们经常会将现实中的模拟信号,通过 ADC 转换为数字信号进行运算、传输、储存,再通过 DAC 转换为模拟信号,呈现出来。

但要注意的是,现实中的模拟量连续的,意味着它有无限的分辨率,但转换为数字量之后,将会丢失一定的精度,在时间和幅度上都会变成离散的值。

ADC 基本原理

ADC(Analog-to-Digital Converter)指模拟 / 数字转换器,可将真实世界的模拟信号,例如温度、压力、声音或者图像等,转换成更容易储存、处理和发射的数字形式。

采样

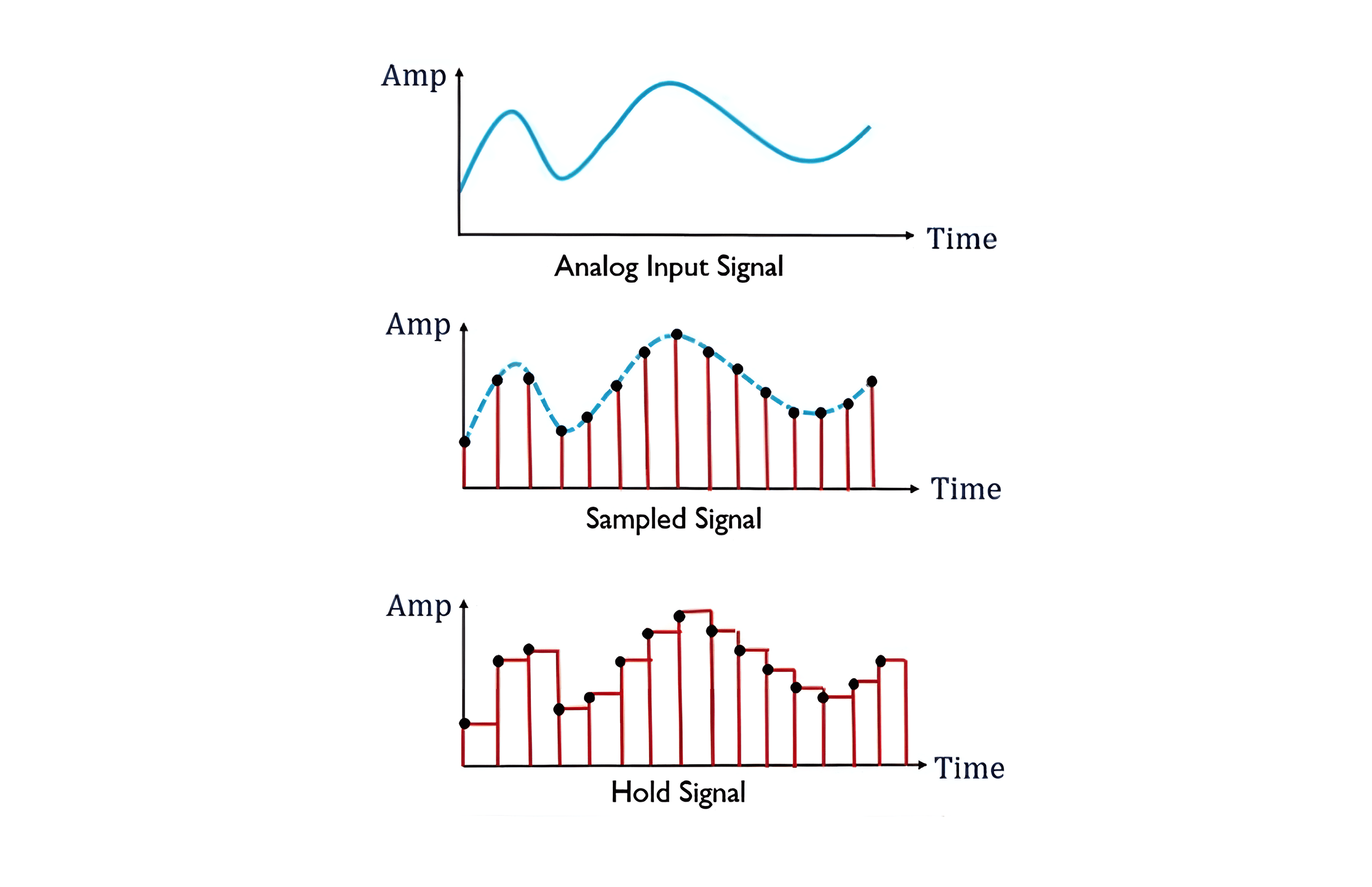

因为输入的模拟信号是连续的,而将要输出的数字信号是离散的,所以只能进行瞬时采样,再将采样值转换为输出的数字量,再重新开始下一轮的采样。

为了能准确无误用信号 表示出模拟输入信号 ,至少需要满足采样定理,即采样频率 在模拟输入信号最高频率分量 的 2 倍以上(通常会取 3~5 倍,但太高的频率需要更快的工作速度,需要综合成本考虑):

只要满足了采样定理,即可用低通滤波器,将 还原为 。滤波器电压传输系数应在低于 时保持不变,在 前迅速下降为 0。

保持

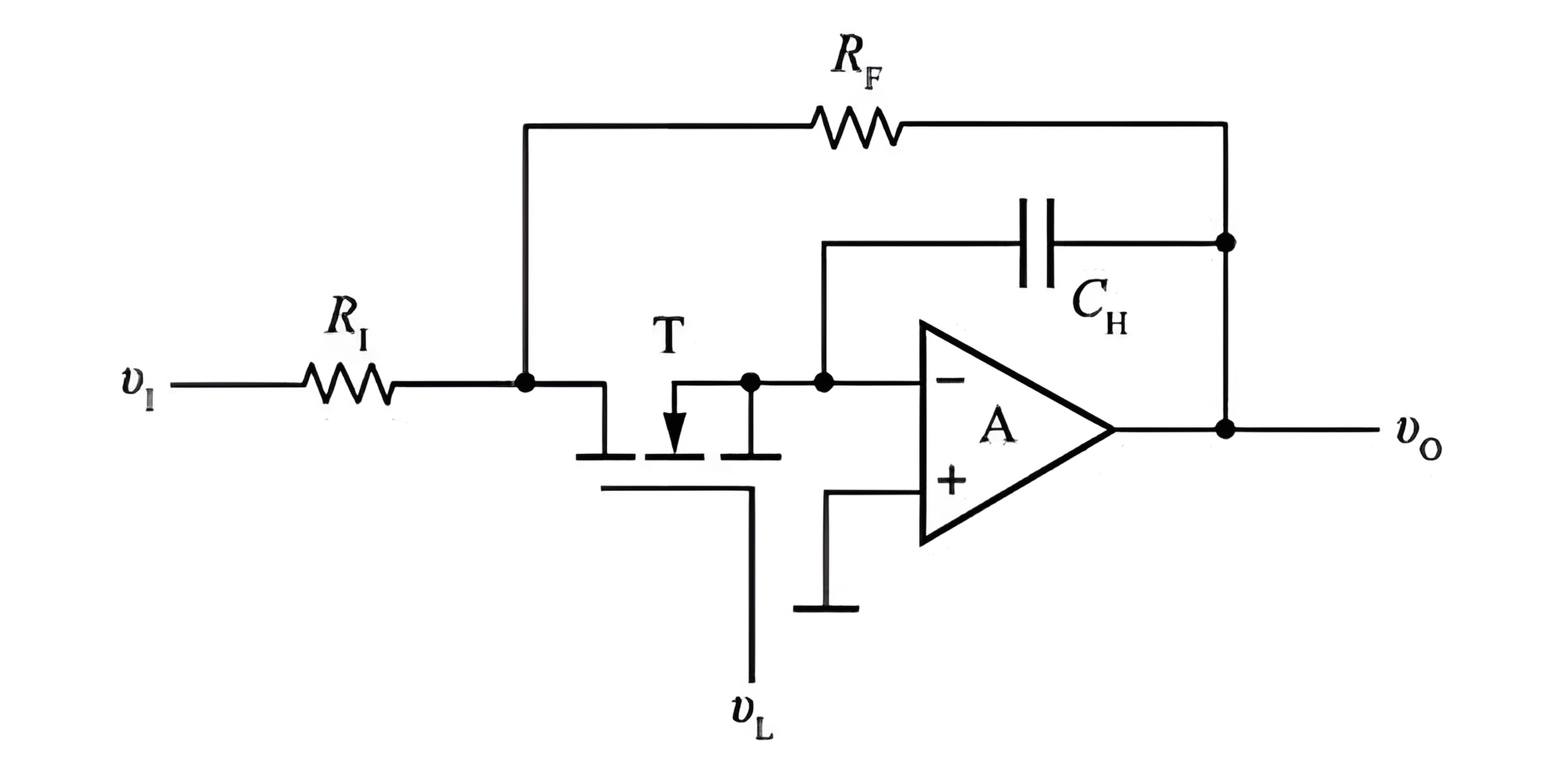

保持电路能够采样结束后,让信号保持一段时间,使 ADC 有充分时间进行转换。一般采样脉冲频率越高、采样越密,采样值就越多,采样保持电路的输出信号就越接近输入信号的波形。采样 - 保持电路的基本形式如下:

采样 - 保持的基本步骤:

- 当采样控制信号 为高电平时,使 MOS 管 导通, 经过电阻 和 MOS 管 ,给电容 充电。

- 若取 ,则充电结束后 。

- 当采样控制信号 跌落回电平时,MOS 管 截止,电容 上的电压不会突变,所以 也能保持一段时间,采样结果得以被记录下来。

量化

采样得到的数字量,必须为某个规定的最小数值单位的整数倍,这个转换过程称为量化,所取的最小数量单位称为量化单位 。数字信号最低有效位 LSB 的 1 所代表的数量大小就等于 。

因为模拟电压是连续的,不一定能被 整除,因此会出现量化误差。

量化级越细,量化误差就越小,所用二进制代码的位数就越多,电路也越复杂。

编码

将量化的结果用二进制(或其他进制)表示出来,称为编码。

ADC 常见类型

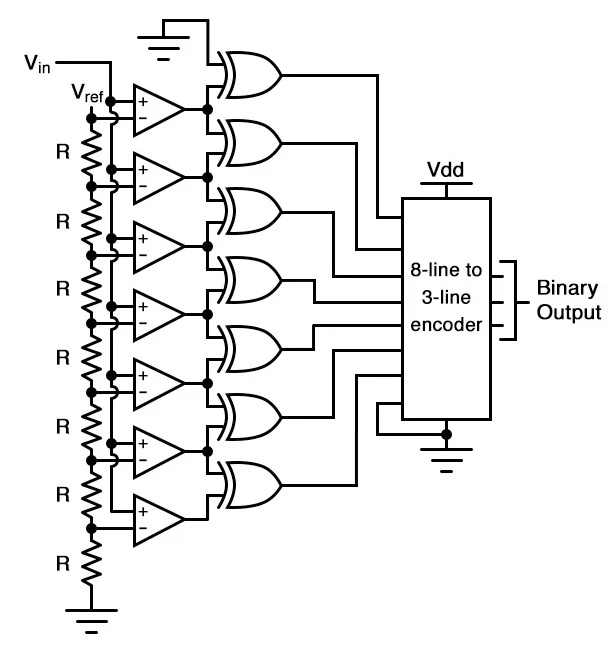

并联比较型(Flash)

并联比较型 ADC 又称 Flash ADC,属于直接 ADC,能将输入的模拟电压直接转换为输出的数字量,不需要经过中间变量转换。它由一系列电压比较器组成,每个比较器将输入信号与唯一的分压后的参考电压进行比较。比较器的输出连接编码器电路的输入,产生二进制的输出。

不仅在操作理论方面是最简单的,而且在速度方面也是最有效的 ADC 技术,仅受比较器和栅极传播延迟的限制。不幸的是,对于任何给定数量的输出位,它是最密集的组件

并联比较型 ADC 的转换速度是最快的,但缺点是需要使用很多电压比较器和大规模的代码转换电路(常见的并联比较型输出大都在 8 位以下)。

逐次逼近型

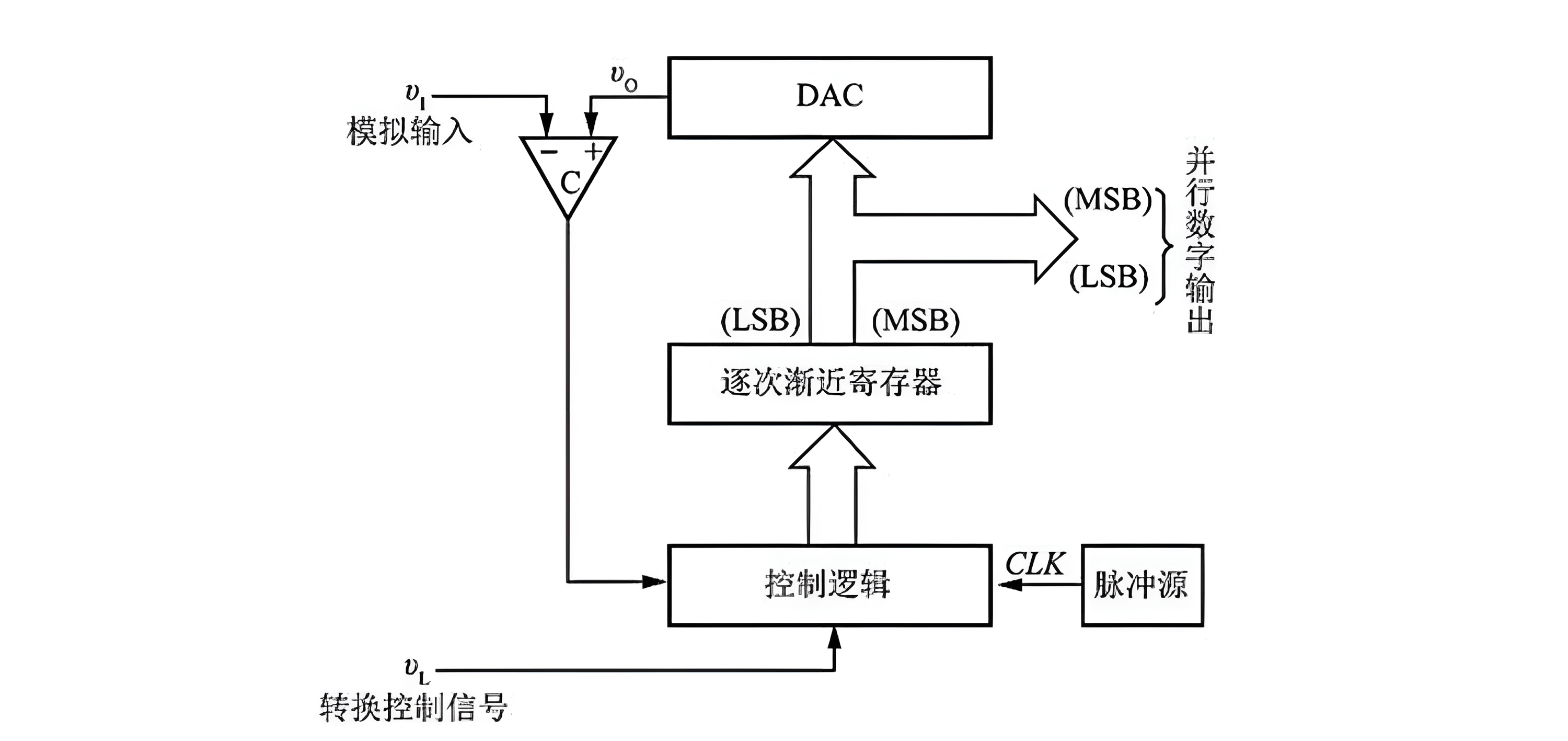

逐次逼近型(Successive Approximation)ADC 采用的是一种反馈比较型电路结构。由比较器、DAC、寄存器、时钟脉冲源和控制逻辑等组成:

其原理是,设定一个数字量,通过 DAC 得到一个对应的输出模拟电压。将这个模拟电压和输入的模拟电压信号从最高位开始顺序地相比较,如果两者不相等,则调整所取的数字量,直到两个模拟电压相等为止,最后所取的这个数字量就是所求的转换结果。其过程像用天平去称量位置重量的物体,先加大砝码,再逐次添加或换用小砝码。

逐次逼近型 ADC 的优点是速度高,功耗低,在低分辨率(12 位)下具有性价比优势;缺点是转换速率一般,电路规模中等。

双积分型(V-T)

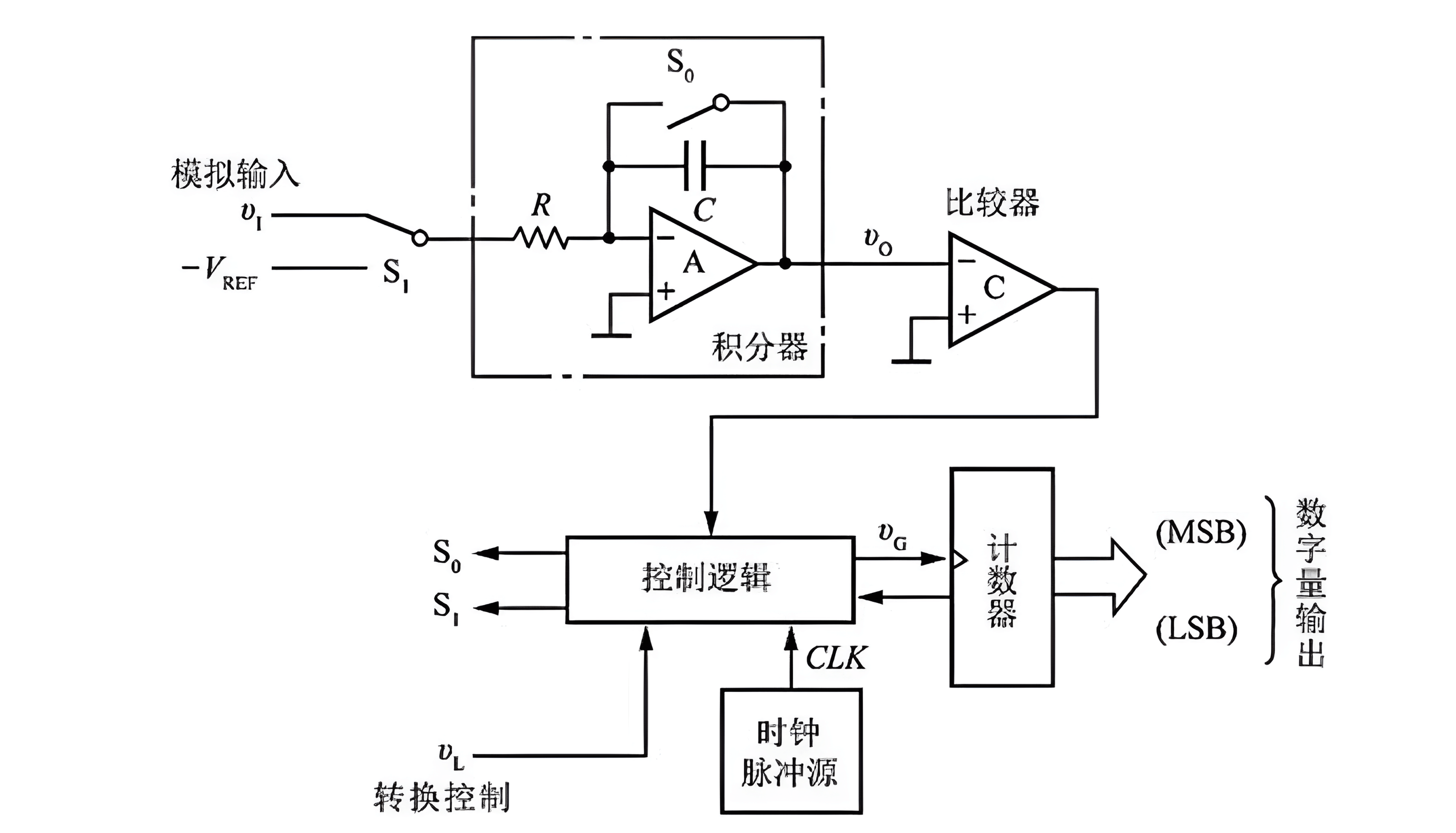

双积分型 ADC 是一种间接 ADC,它首先将输入的模拟电压信号转换成与之成正比的时间宽度信号,随后在此时间宽度内,对固定频率的时钟进行脉冲计数,计数的值就是正比于模拟输入电压的数字信号。因此,也将这种 ADC 称为电压 - 时间变换型(V-T)ADC。

双积分型 ADC 由积分器、比较器、计数器、控制逻辑和时钟信号源组成,如图:

双积分型 ADC 的优点是工作性能稳定(两次积分,排除 RC 参数差异)、抗干扰能力强(积分受噪声影响不大);缺点是转换速率低(转换精度依赖于积分时间)。

Σ-Δ 型

Σ-Δ 调制型 ADC 的原理与上文的并联型与逐次逼近型 ADC 不同,它不是将采样信号的绝对值进行量化编码,而是将两次相邻采样值之差(增量)进行量化与编码的。其基本结构如下:

它由线性电压积分器、1 位输出量化器、1 位输入 DAC 和一个求和电路组成。经过量化器处理输出的数字信号 ,经过 DAC 转换为模拟信号 ,并负反馈至输入端的求和电路,与输入信号 相减,得到差值 。积分器对 作线性积分,输出电压 至量化器,由量化器量化为 1 位的数字量输出。由于采用 1 为输出的量化器,所以在连续工作的状态下,输出信号 是由 0 和 1 组成的数据流。

Σ-Δ 调制型 ADC 的优点是可以容易地做到高分辨率测量;缺点是转换速率低、电路规模大。

电压 - 频率变换型(V-F)

电压 - 频率变换型(V-F)ADC 是一种间接 ADC。主要由 V-F 变换器(也称为压控振荡器 Voltage Controlled Oscillator,简称 VCO)、计数器及其时钟信号控制闸门、寄存器、单稳态触发器等几部分构成:

其原理是:

- 将输入的模拟电压信号转换为对应的频率信号。

- 在固定的时间内对频信号率计数。

- 计数结果正比于输入电压的幅值。

ADC 主要参数

- 分辨率:输出数字量变化一个相邻数值所需输入模拟电压的变化量,一般用二进制的位数表示,分辨率为 n 表示是满刻度 Fs 的 2 的 n 次方分之一。

- 量化误差:ADC 的有限位数对模拟量进行量化而引起的误差。要准确表示模拟量,ADC 的位数需要很大甚至无穷大,所以 ADC 器件都有量化误差。一个分辨率有限的 ADC 的阶梯状转换特性曲线与具有无限分辨率的 ADC 转化特性曲线之间的最大偏差就是量化误差。

- 转换速率:每秒进行转换的次数。

- 转换量程:ADC 所能测量的最大电压,一般等于参考电压,超过此电压有可能损毁 ADC。当信号较小时可以考虑降低参考电压来提高分辨率,改变参考电压后,对应的转换值也会改变,计算实际电压时需要将参考电压考虑进去,所以说一般参考电压都要做到很稳定且不带有高次谐波。

- 偏移误差:ADC 输入信号为 0 时,但 ADC 转换输出信号不为 0 的值。

- 满刻度误差:ADC 满刻度输出时对应的输入信号与理想输入信号值之差。

- 线性度:实际 ADC 的转移函数和理想直线的最大偏移。

DAC 基本原理

DAC(Digital-to-Analog Canverter),指数字 / 模拟转换器。可将数字量转换为成比例的模拟电压或电流。举个例子,计算机可能产生范围从 00000000 到 11111111 的数字输出,DAC 将其转换为范围从 0 到 10V 的电压。DAC 从基本原理上可以分两类:电流求和型、分压器型。

DAC 常见类型

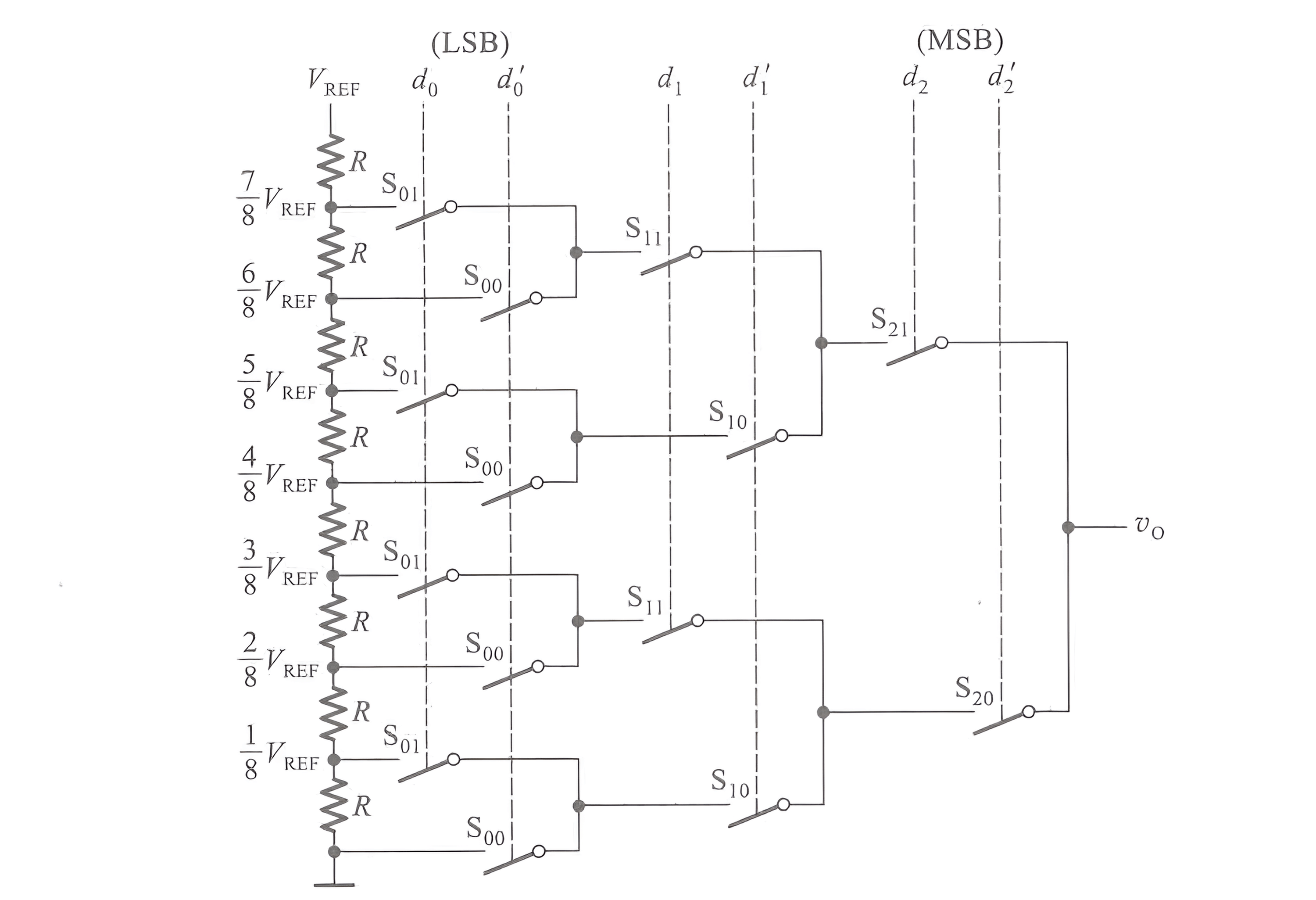

开关树型

开关树型 DAC 是最简单粗暴的 DAC,由电阻分压器和树状的开关网络组成:

这些开关分别受 3 位输入 控制,由此可得:

进一步看,对于 n 位二进制输入的开关树型 DAC,输出为:

开关树型 DAC 特点是电阻种类单一,且在输出端基本不取电流的情况下,对开关导通电阻要求不高;但缺点是用的开关太多。

权电阻网络

权指的是一个多位二进制数中,每一位 1 所代表的数值。例如,一个 n 位二进制数 从最高位(Most Significant Bit, MSB)到最低位(LSB)的权依次为 。

权电阻网络型 DAC(属于电压输出型)的原理如下图所示(4 位),它由权电阻网络,4 个模拟开关和 1 个求和放大器组成:

其中, 是 4 个电子开关,受 4 个信号的控制,输入为 1 时开关拨到 ,输入为 0 时开关接地。所以,当 时有之路电流 流向求和放大器, 时之路电流为零。求和放大器是一个负反馈放大器,当反相输入端 的电位低于同相输入端的电位 时,输出端对地电压 为正;当 时, 为负。且当 稍高于 时,即可在 产生大幅度的负输出电压。 经 反馈回 ,使得 降低回 (0V)。

假设运算放大器为理想器件(输入电流为零),则可得到:

又因为 ,因此各支路电流分别为:

其中, 可取 0 或 1。代入上式,并假设反馈电阻 时,可得到输出电压:

进一步看,对于 n 位权电阻网络 DAC,当反馈电阻 时,输出电压计算公式是:

所以,输出的模拟电压正比于输入的数字量 ,其变化范围是 0 至 。另外一方面,如果需要得到正输出电压,则应该提供负的 。

权电阻网络型 DAC 的优点是结构简单,但缺点是个电阻阻值相差较大,在现实中有可能造成比较大的精度差。为了改善,可以采用双极权电阻网络,此处不展开说明,但仍无法从根本上解决。

倒 T 形电阻网络

为了改善权电阻网络 DAC 阻值相差太大的问题,可以采用倒 T 形电阻网络 DAC,它只用了 R 和 2R 两种阻值的电阻(所以也称为 R2R DAC),对于控制精度有很大的帮助:

当求和放大器反馈电阻阻值为 R 时,输出电压:

可见,倒 T 形电阻网络与权电阻网络 DAC 的计算公式是相同的。

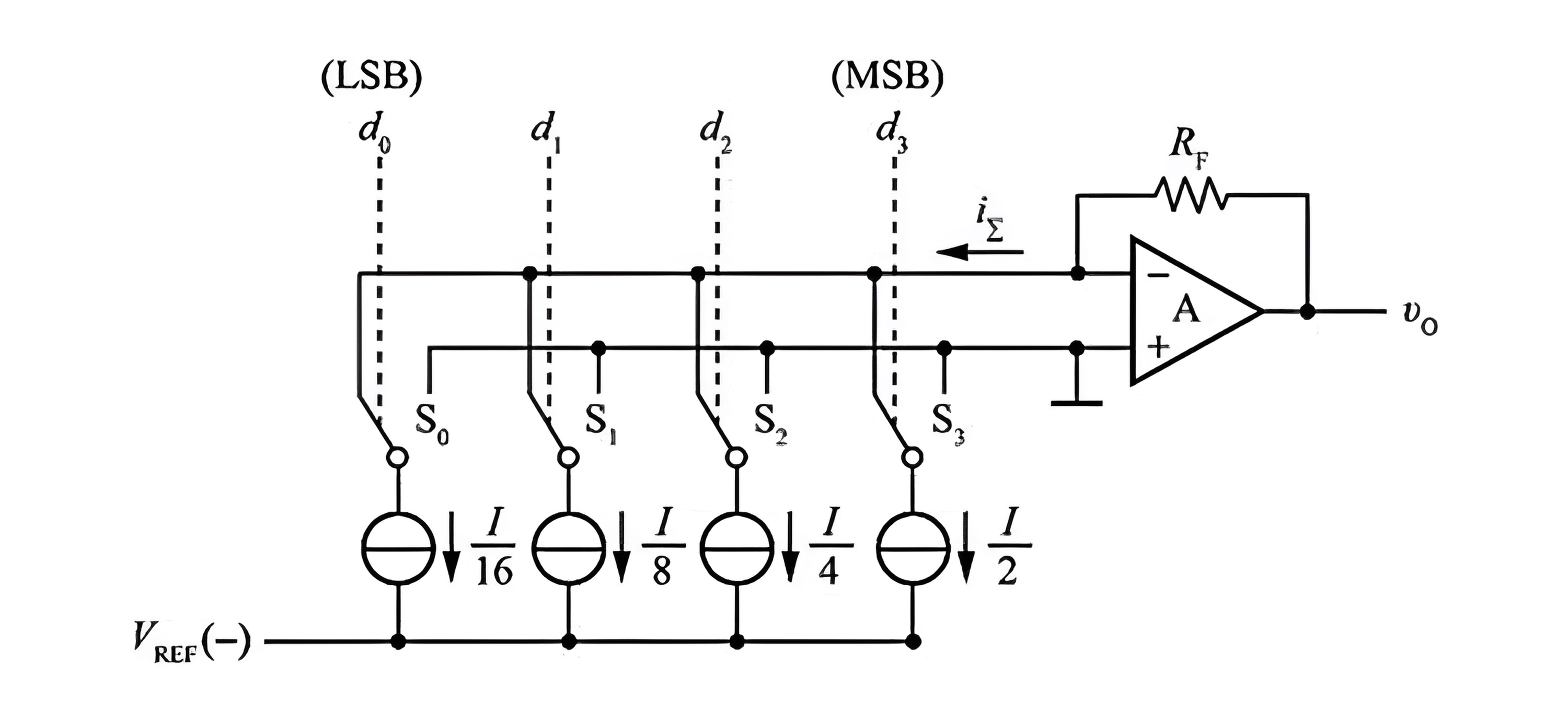

权电流型

在分析权电阻网络与倒 T 形电阻网络时,会将模拟开关当理想器件看待,但实际中它们存在一定的导通电阻和压降,开关之间的一致性又有差别,所以会产生转换误差而影响精度。解决方法是采用权电流型 DAC,它有一组恒流源,每个恒流源电流大小依次为前一个的一半,与输入二进制对应位的权成正比。采用恒流源使得每个支路电流大小不再受开关导通电阻和压降的影响。

当输入数字量的某位为 1 时,对应的开关将恒流源接至运算放大器的输入端;当输入代码为 0 时,对应的开 关接地,故输出电压为:

DAC 主要参数

- 分辨率:最小输出电压(也就是输入数字量为 1 时的电压)与最大输出电压(也就是输入数字量为最大,每一位都是 1 时的电压)之比。一般通过输入数字量的位数来表示。

- 转换量程:DAC 能输出的最大电压,一般的关于参考电压或其倍数。

- 建立时间:从输入数字量到输出模拟量之间的延时时间。

- 转换精度:与 ADC 的转换精度类似。

参考与致谢

- 《ADC/DAC 应用设计宝典》

- 数模转换与模数转换

- ADC and DAC (Analog to Digital And Digital to Analog Converters)

- 漫谈 DAC 原理

- 《Analog Engineer’s Pocket Reference》

- 《数字电子技术(第六版)_阎石》

本篇文章受 CC BY-NC-SA 4.0 协议保护,转载请注明出处。