半导体测试基础 - 功能测试

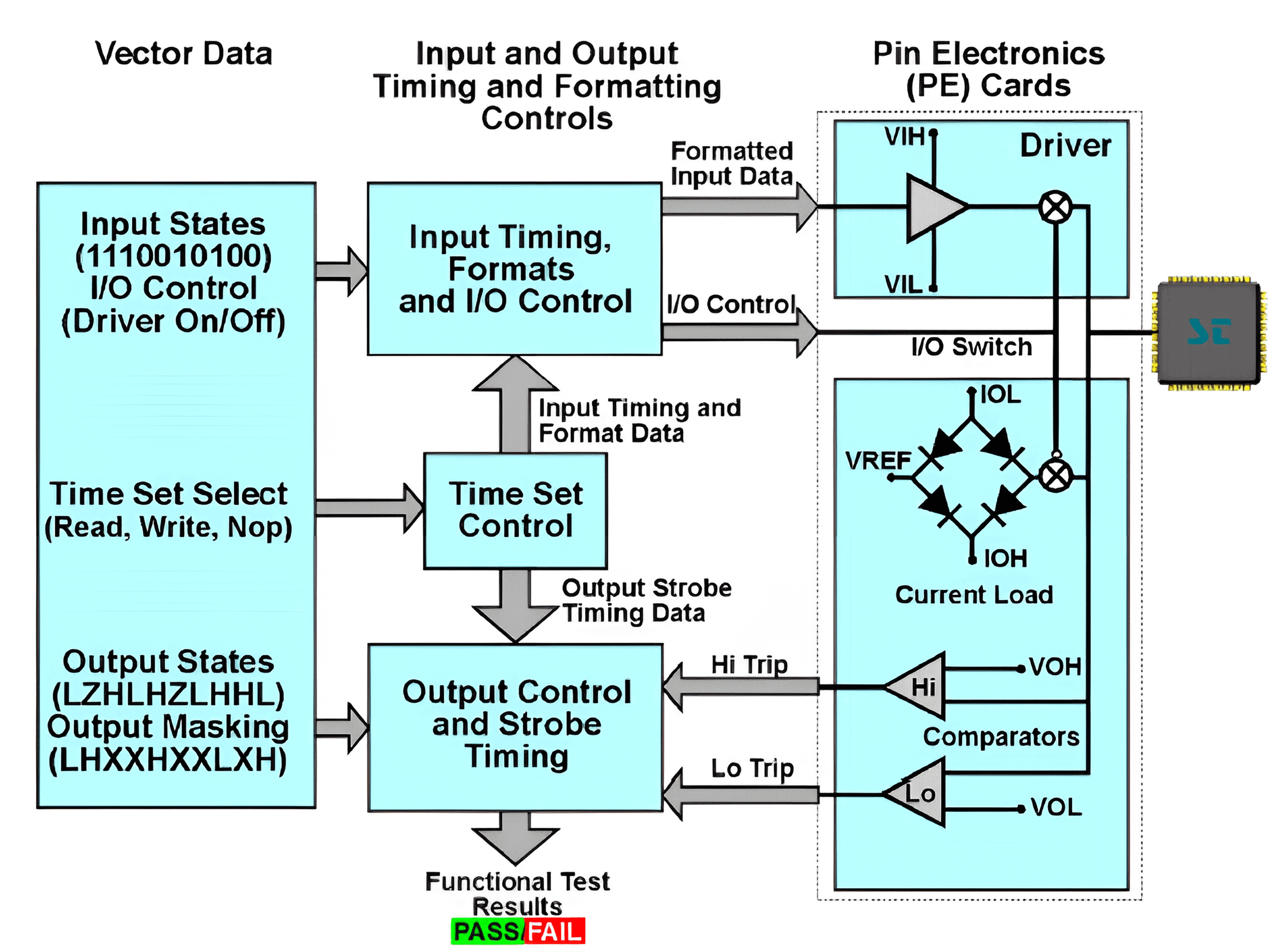

功能测试(Functional Test)主要是验证逻辑功能,是运用测试矢量和测试命令来进行的一种测试,相比于纯 DC 测试而言,组合步骤相对复杂且耦合度高。

在功能测试阶段时,测试系统会以周期为单位,将测试矢量输入 DUT,提供预测的结果并与输出的数据相比较,如果实际的结果与测试矢量预测值不相符,则认为不通过。

基本概念

测试矢量(Test Vectors)

测试矢量也称测试模式(Test Pattern),可以理解为器件被设计逻辑功能的输入输出真值表。Test Vectors 强调时序,一般是一系列输入输出的组合。一般用 0/1 表示输入低 / 高电平,用 L/H/Z 表示输出低电平 / 高电平 / 高阻态,用 X 表示既无输入也无输出。

总功能测试

各种参数的功能测试法

OS 测试 - 功能测试法

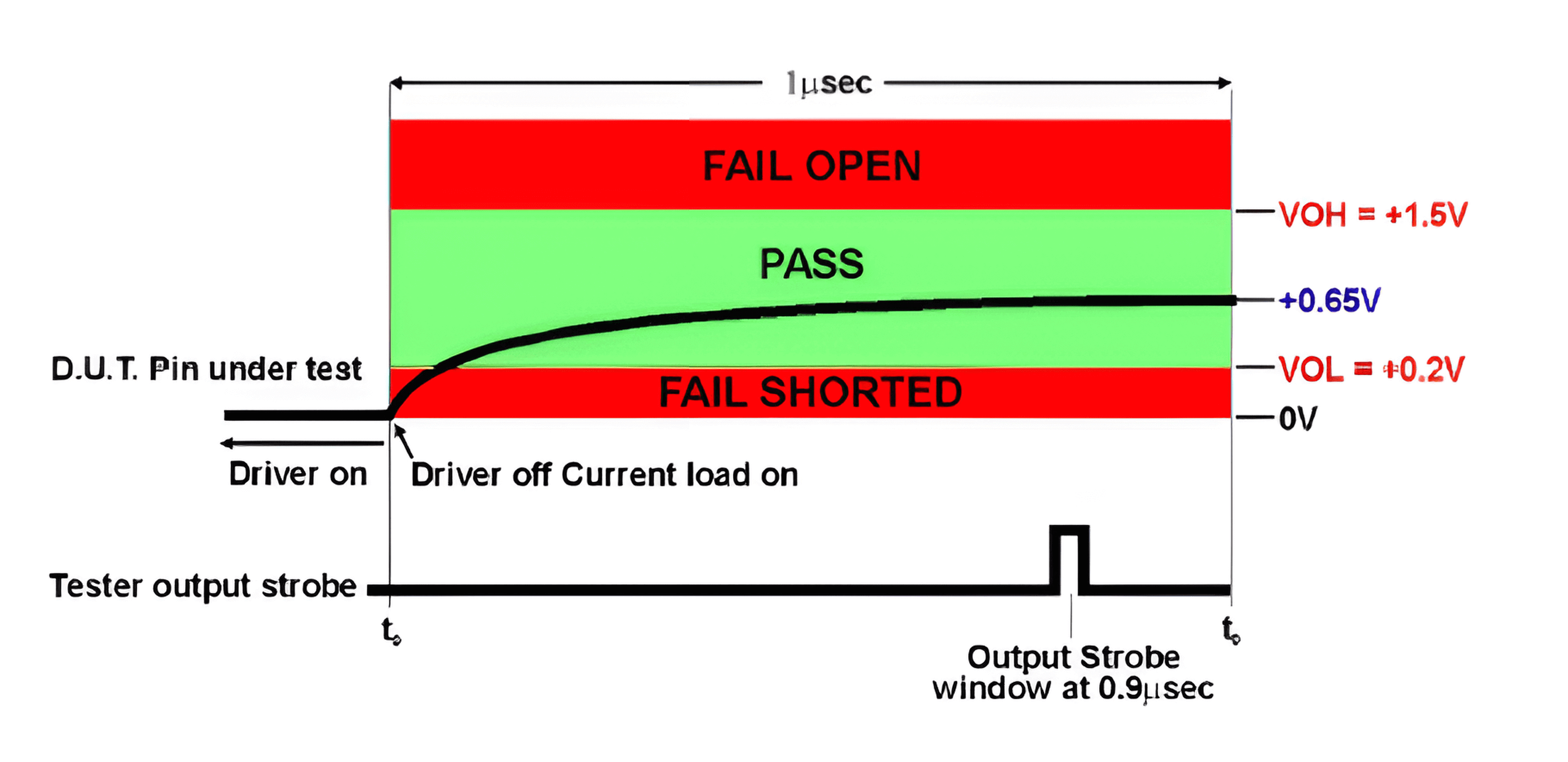

开短路不属于功能,但也可以用功能测试的方法进行测试,关闭 PMU 和 Driver,用 Current Load 和 Voltage Receiver 进行测试。测试示意图如下:

测试流程如下:

- 将除待测引脚外的所有引脚接地(电源和信号引脚)。

- 定义 VOL/VOH(比如 0.2V/1.5V)。

- 将待测引脚设置为输出模式,并关断此引脚(高阻 Z)。

- 提供 VREF(3V),形成动态负载电流(约 400µA),检测引脚上的电压

- 高于 VOH(+1.5V):Fail(Open)

- 低于 VOL(+0.2V):Fail(Short)

- 高阻态(正偏后的压降约 0.65V):Pass

- 复位引脚状态,接着测下一个引脚。

本测试的矢量模式示例如下:

00000 /* cycle 1 将所有引脚接地 */

Z0000 /* cycle 2 测试第 1 个引脚的保护二极管 */

0Z000 /* cycle 3 测试第 2 个引脚的保护二极管 */

00Z00 /* cycle 4 测试第 3 个引脚的保护二极管 */

000Z0 /* cycle 5 测试第 4 个引脚的保护二极管 */

0000Z /* cycle 6 测试第 5 个引脚的保护二极管 */

/* 下一个周期将会被单独执行 */

ZZZZZ /* cycle 7 关断所有引脚并测试它们 */

正常引脚电压变化与采样的示意图如下。采样窗口设置在 0.9µs、持续时长 0.01µs 是为了让电压上升到稳定再采样:

接下来测对地保护二极管。只需要测是否开路(如果由短路的情况,那必然过不了前面的测试)。功能测试法测对地二极管的示意图如下:

这次的矢量测试,只需跑一次前面的第 7 个周期(ZZZZZ),即可并行测试所有对地二极管。

(拉低引脚和地用的是 DPS;如果 Fail Open 的话,测出来的电压是 VREF 而非钳位电压,不要跟 DC 方法搞混了。)

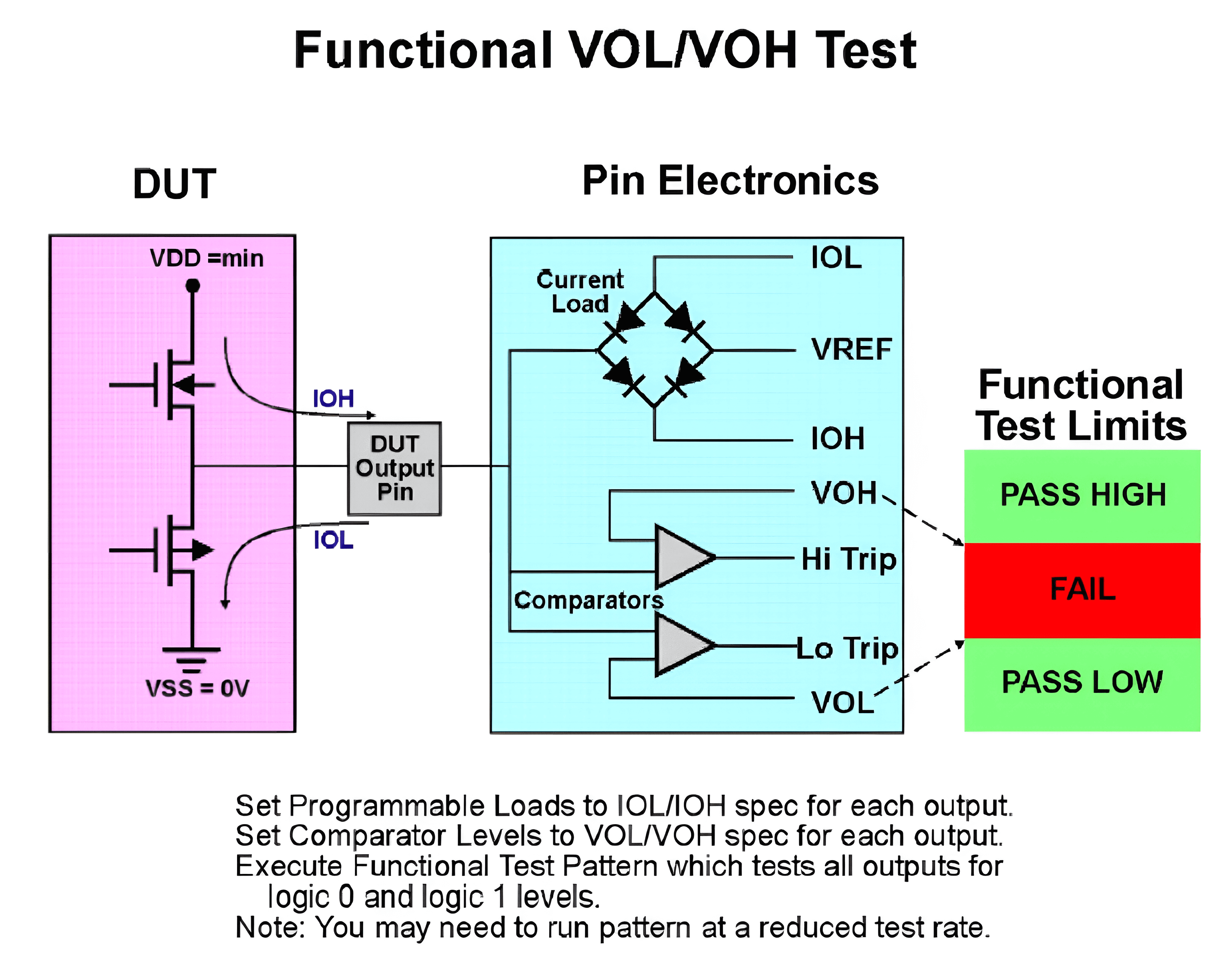

VOL/IOL & VOL/IOH 测试 - 功能测试法

测试示意图如下:

测试流程如下:

- 供电 VDDmin(??)。

- 设置 VREF(量程中间值),将形成动态负载电流。

- 执行功能测试,监控引脚的电压

- 低于 VOH Spec 或高于 VOL Spec:Fail

- 高于 VOL Spec:Fail

- 其他区间:Pass

VIL/VIH 测试 - 功能测试法

VIL/VIH 是看 DUT 能不能正常识别输入的逻辑。用功能测试法测 VIL/VIH 的示意图如下(假设此芯片左边是输入引脚,右边是输出,输入输出逻辑电平同相):

用功能测试法测 VIL/VIH 的流程是:

- 首先要供 VDDmax 的电源给 DUT。

- 按照 VIL/VIH 标称值给引脚输入电压,让其他的参数满足一定余量。

- 执行功能测试,监控输出引脚的电压

- 低于 VOH Spec:Fail

- 高于 VOL Spec:Fail

- 其他区间:Pass

- 供 VDDmin 的电源给 DUT,并重复以上的流程。

如果遇到测试不通过的情况,如果不能定位到错误所在,可以先给多一点余量,排除因其他因素导致的问题。比如给 VIL 最优低电平(0V),给 VIH 最优高电平(VDD),看看是否能按流程通过测试,随后再逐步赋 VIH/VIL 原始值以排除问题。

IOZL/IOZH 测试 - 功能测试法

使用功能测试法测试 IOZL/IOZH 的示意图如下:

测试流程如下:

- 给 DUT 供电 VDD,设置比较器的值为 VOL/VOH。

- 设置 VREF,形成动态负载电流,测引脚电压

- 高于 VOH Spec:Fail

- 低于 VOL Spec:Fail

- 其他区间:Pass

参考与致谢

- 《The Fundamentals Of Digital Semiconductor Testing》

- 《DC Test Theory》

本篇文章受 CC BY-NC-SA 4.0 协议保护,转载请注明出处。